# Class notes : APE,

# Prepared By: Dr.Shaikh Mohammed Suhel (Ph.D, M.Tech, Gate, B.E) Associate Professor and Department Head

## Multilevel Inverter

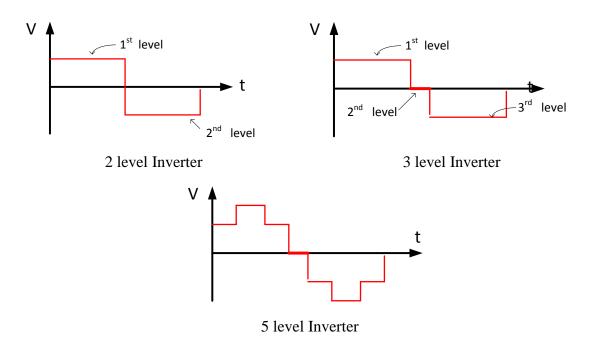

**Definition:** The number of steps in the voltage of the output terminal with respect to any arbitrary internal reference point.

> Generated stepped waveform output voltage with adjusted frequency and amplitude.

### Question: Why Multilevel Inverter is required? Or Difference between two level and Multilevel Inverter

| 2 Level Inverter                                                                                                          | Multilevel Inverter                                                                                                                       |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1) The stress on the device is high in case of<br>two level inverter as $\frac{dv}{dt}$ is high in this<br>configuration. | 1) The stress on the device is low as voltage increases in stepped manner and so that $\frac{dv}{dt}$ is lower in this type configuration |  |  |

| 2) Higher voltage operation is difficult                                                                                  | 2) Higher voltage operation is easily                                                                                                     |  |  |

- 3) Filter size requirement is higher in two level

- As power level increases, dc link voltage and switching frequency has to be reduced. This action lead to generate lower order harmonics (7<sup>th</sup> and 9<sup>th</sup>)

- 5) Devise rating is high in case of 2 level inverter

possible as voltage is distributed among the series connected switches

- 3) MLI (Multi level Inverter) reduces the filter size requirement

- 4) MLI reduces the lower order harmonics and operates with lower switching frequencies

- 5) Device rating reduces significantly and this will reduces the cost of MLI

#### **Types of MLI:**

- 1) Diode clamped MLI or Neutral Point Clamped (NPC) MLI

- 2) Flying capacitor type MLI

- 3) Cascade H-Bridge MLI

Diode Clamped MLI:

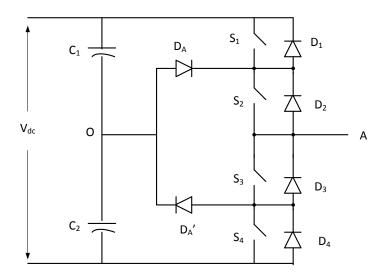

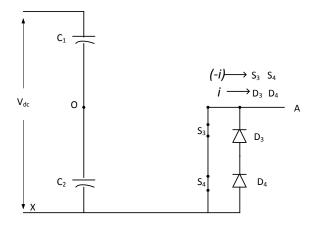

Three level Diode Clamped MLI:

- ➢ Fig. 1 shows the one leg of Inverter (total three legs of three phase)

- No of Capacitor require= (N-1) =2 ; where N is the level of Inverter No of switches required/phase= 2(N-1) =4 Any times switches 'ON'= (N-1) =2

Fig.1: 3-Level Diode clamped MLI

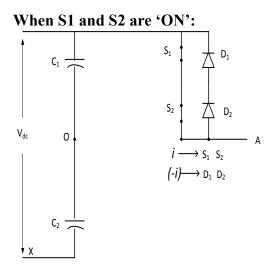

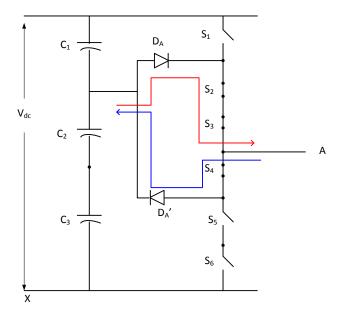

#### When S<sub>2</sub> and S<sub>3</sub> are 'ON':

- $\succ$  Here,  $V_{ax}=V_{dc}$  and  $V_{ao}=V_{dc}/2$ ;

- The positive direction of current flows through -C<sub>2</sub>-C<sub>1</sub>-switch S<sub>1</sub> and S<sub>2</sub>

- The negative direction of current (Load to source) flows through diode D<sub>1</sub> and D<sub>2</sub>-C<sub>1</sub>-C<sub>2</sub>

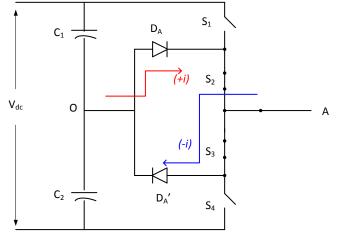

- $\blacktriangleright$  Here,  $V_{ax} = V_{dc}/2$  and  $V_{ao} = 0$ ;

- The positive direction of current flows through -D<sub>A</sub>-switch S<sub>2</sub>

- The negative direction of current (Load to source) flows throughswitch S<sub>3</sub>-and D<sub>A</sub>'

When S<sub>3</sub> and S<sub>4</sub> are 'ON':

- $\succ$  Here,  $V_{ax}=0$  and  $V_{ao}= V_{dc}/2$ ;

- The positive direction of current flows through -C<sub>1</sub>-C<sub>2</sub>-diode D<sub>4</sub> and D<sub>3</sub>

- The negative direction of current (Load to source) flows through switch S<sub>3</sub>-S<sub>4</sub> and -C<sub>2</sub>-C<sub>1</sub>

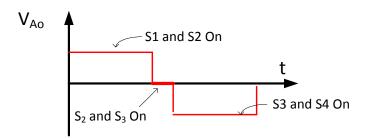

Fig.2: Output Pole Voltage VAO

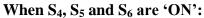

| Switching sta | te of 3 level | Inverter: |                       |       |                     |                 |

|---------------|---------------|-----------|-----------------------|-------|---------------------|-----------------|

| Switching     | $S_1$         | $S_2$     | <b>S</b> <sub>3</sub> | $S_4$ | V <sub>AO</sub>     | V <sub>AX</sub> |

| state         |               |           |                       |       |                     |                 |

|               | ON            | ON        | OFF                   | OFF   | $V_{dc}/2$          | V <sub>dc</sub> |

|               | OFF           | ON        | ON                    | OFF   | 0                   | $V_{dc}/2$      |

|               | OFF           | OFF       | ON                    | ON    | -V <sub>dc</sub> /2 | 0               |

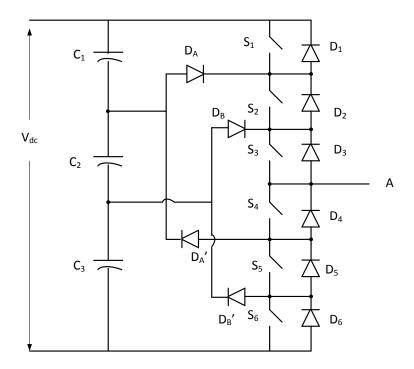

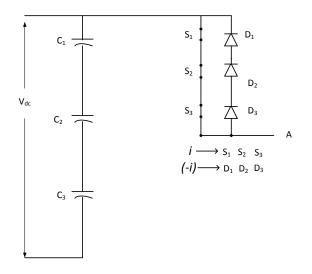

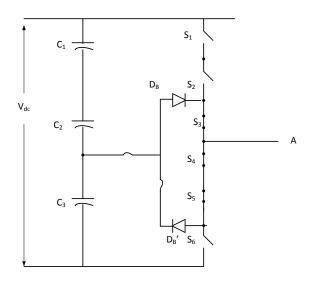

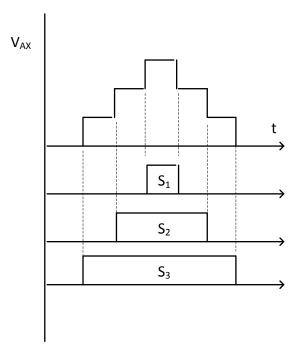

### Four level Diode Clamped MLI:

- Fig. 4 shows the one leg of Inverter (total three legs of three phase)

- No of Capacitor require= (N-1) =3; where N (=4) is the level of Inverter No of switches required/phase= 2(N-1) =6 Any times switches 'ON'= (N-1) =3

When S<sub>1</sub>, S<sub>2</sub> and S<sub>3</sub> are 'ON':

- $\blacktriangleright$  Here,  $V_{ax}=V_{dc}$ ;

- The positive direction of current flows through C<sub>3</sub>-C<sub>2</sub>-C<sub>1</sub>-switch S<sub>1</sub> S<sub>2</sub> and S<sub>3</sub>

- The negative direction of current (Load to source) flows through diode D<sub>1</sub> D<sub>2</sub> and D<sub>3</sub>-C<sub>1</sub>-C<sub>2</sub>-C<sub>3</sub>

When S<sub>2</sub>, S<sub>3</sub> and S<sub>4</sub> are 'ON':

- > Here,  $V_{ax}=2V_{dc}/3$ ;

- The positive direction of current flows through D<sub>A</sub>-switch S<sub>2</sub> and S<sub>3</sub>

- The negative direction of current (Load to source) flows through S<sub>4</sub> diode D<sub>A</sub>'

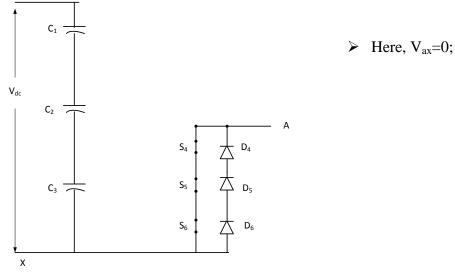

When S<sub>3</sub>, S<sub>4</sub> and S<sub>5</sub> are 'ON':

- $\blacktriangleright$  Here,  $V_{ax}=V_{dc}/3$ ;

- The positive direction of current flows through D<sub>B</sub>-switch S<sub>3</sub>

- The negative direction of current (Load to source) flows through S<sub>4</sub> S<sub>5</sub>diode D<sub>B</sub>'

# Features of NPC MLLI (or Diode Clamped MLI):

- ➤ In 4 Level NPC MLI D<sub>A</sub> has to block 1/3 V<sub>dc</sub> (Rating)

- $\succ$  D<sub>A</sub>' has to block 2/3 V<sub>dc</sub>

- Separate heat sink required in this case

- Voltage unbalance issue: When o/p voltage is Vdc: C1, C2, C3 supply the power and When o/p voltage is 2/3 Vdc C2, C3 supply the power-> so voltage across C1 increases compare to other two capacitors.

Fig.4: Output Voltage V<sub>AX</sub>

### Advantages:

- ➢ Filter size reduces

- All switches operate at fundamental frequency so switching losses are reduced and efficiency increase.

- > Control Method is simple

#### **Disadvantage:**

> When no of level increases, no of clamping diode increases.